The Sparta core example is located in sparta/example/CoreModel.

Example Core Layout

The CoreExample is an example Sparta simulator that uses the Sparta framework to mimic a very rudimentary model of a simple out-of-order core. The model does not have dependency checking nor actually renames any instructions. The "ISA" used is a few random instructions pulled from the PowerPC ISA listed in a table in Fetch.cpp.

For a more concrete core performance model, check out the RISC-V Performance Model based on Sparta: https://github.com/riscv-software-src/riscv-perf-model

The example touches on Sparta command line simulation, construction phasing, unit creation, port creation and binding, event creation, and data transfer.

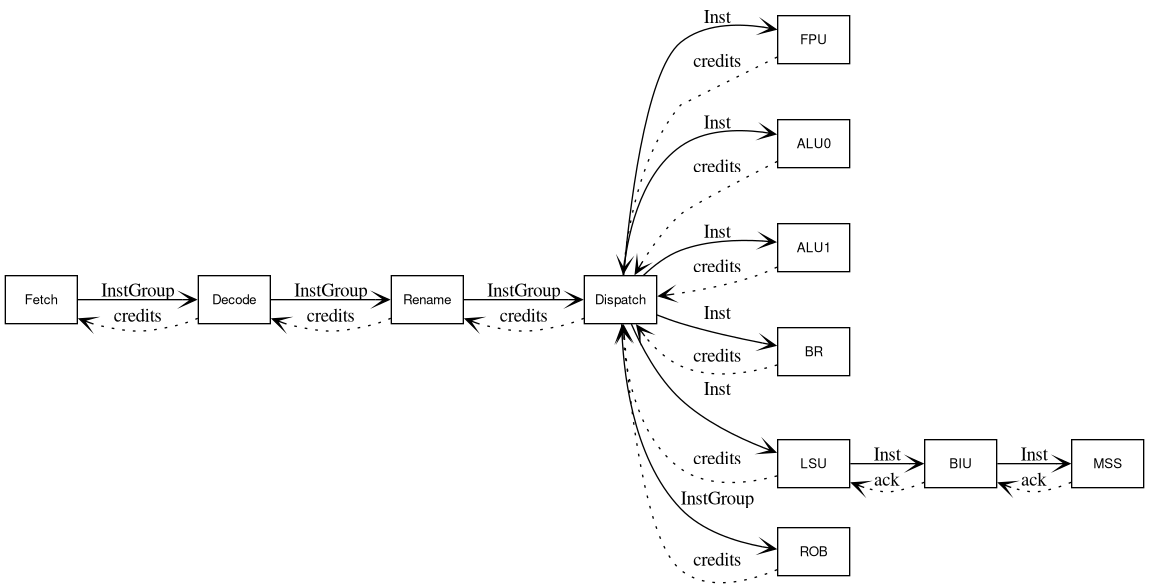

The ExampleCore has a simple pipeline:

This heirarchy is built in core_example::ExampleSimulator::buildTree_ pulling resources and factories from core_example::CoreTopology_1.

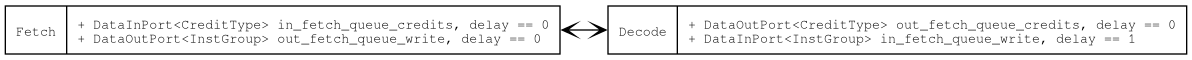

Instructions are created in Fetch and progression of these instructions is based on a credit system. Credits flow from ROB through Dispatch though Rename, etc. in 0 time (dotted lines) while instructions flow from Fetch to Decode to Rename, etc (solid lines) in a delay of 1 cycle. This flow is controlled based on the rule (adopted by this example) that all DataInPorts<core_example::InstGroup> take objects delayed by 1 cycle (set at instantiation time) and all credit DataInPorts<uint32_t> are assumed to be 0 cycle. For example:

These ports are bound in core_example::ExampleSimulator::bindTree_, using the port_connections list defined in core_example::CoreTopology_1. The ports themselves are instantiated in Fetch.cpp / Fetch.hpp and Decode.cpp / Decode.hpp.

Without the delay of 1 cycle on the in_fetch_queue_write, we will come across a cycle in simulation:

Adding the cycle delay:

The entire core example follows this paradigm.

Building

To build the CoreExample, simply type make in the example/CoreModel directory.

Refer to builtin help for up-to-date help and commands, but try running the model with the '-h' option.

Most of the commands listed in the help are directly from the Sparta framework and not sparta_core_example. These are "free" commands the framework provides (via sparta::app::CommandLineSimulator). The modeler is not required to use this class for simulation.

Invocations

Running/Configuring

Dump out the parameters:

Read in parameters from a file and/or change via the command line. Parameters are set in the order in which they are read from the command line.

Run for 1 million cycles, incrementing a ctr every 1000 cycles. Consume the config file test.yaml and produce a final yaml file called final.yaml. Also, dump the tree:

Debugging/Logging

Enable a Decode "info" log for 1,000 cycles.

Enable a Decode and Fetch "info" log for 1,000 cycles to the same file:

Enable a Decode and Fetch "info" log for 1K cycles after the first 100K cycles:

Enable a Decode and Fetch "info" log for 1K instructions after the first 100K instructions:

Generating Reports

Refer to Report Definition Format (.rrep,.yaml) for more details on Reports.

Dump out a full, simple report report in html:

Dump out a full, simple report with rules. The content is all inclusive of the entire simulation tree (the "" on the command line)

Dump out subset, but simple report with rules. The content is inclusive of the decode tree only for all cores:

Create a ts_report.yaml file to dump out a time-series CSV report (must be run in example/CoreModel directory for the core_stats.yaml file). This is triggered on the stat total_number_retired reaching 3500 insts or greater. It's trigged "on" only once.

Generating Pipeouts

Refer to https://github.com/sparcians/map/tree/master/helios/pipeViewer for directions on building/installing the MAP::Helios::Argos tools preferably using the Conda tools.

Create a 10K instructions Pipeout:

This will create a set of files for the Argos viewer:

Launch the MAP::Helio::Argos viewer (this assumes the correct tools/libaries have been installed). Note that the cpu_layout.alf file is NOT in the build directory of the CoreModel.

The view that pops up is a single-cycle view of the CPU.